스마트폰의 저전력/저복잡 광학식 손떨림 보정(OIS) 컨트롤러를 위한 SoC 설계

Copyright ⓒ 2019 The Digital Contents Society

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-CommercialLicense(http://creativecommons.org/licenses/by-nc/3.0/) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

초록

본 연구는 스마트 폰의 저전력/저복잡 OIS (Optical Image Stabilization) 컨트롤러 SoC 구현을 위한 설계방법을 연구하고 검증했다. 자이로스코프 샘플링 주파수(fs)를 5kHz까지 낮추어도 움직임 추정(ME) 오류는 크게 변화되지 않았다. 자이로 필터는 저복잡도의 BACF/DCF를 ME에 퍼지 알고리즘과 결합하여 성능을 확인하였고, 움직임 보상(MC)에서 제어기/구동기의 동작 주파수(fo)를 5kHz/10kHz로 낮추었으며, PWM 구동은 선형구동 대비 소모전력을 50% 절감하였고, ADC/ DAC의 비트 폭을 11/10비트로 줄일 수 있었다. SoC 설계를 위하여 16비트 DSP 코어를 채택하였고, 자이로 필터, 적분기, 퍼지 블록과 멀티레이트 PID 컨트롤러를 임베디드 SW로 구현하여 면적 및 전력소모를 줄일 수 있었다. 기존 OIS 컨트롤러 SoC와 동등한 면적으로 메모리 및 PWM 구동 등 추가 기능을 탑재하였다. 본 연구의 OIS 컨트롤러 SoC는 기존 대비 동작전류가 30%∼53%감소한 것으로 확인되었다.

Abstract

In this research, several SoC (IC) design approaches are explored and verified, to implement Optical Image Stabilization (OIS) controller SoC, for the low power and complexity of smart phones. The motion estimation (ME) errors are not notably varied above the 5kHz of gyroscope sampling frequency (fs). The gyro filter would yield excellent compensation effects by combining the low complex BACF/DCF with fuzzy algorithm in ME. The operating frequencies (fo) of controller/driver blocks in motion compensation (MC) could be brought down to 5kHz/10kHz. The PWM driving scheme could save 50% of power consumption with respect to linear driving one. Each bit width of ADC/DAC blocks in MC could be reduced to 11bits/10bits. For the SoC design, 16bits DSP core is adopted to architecture. It could reduce the area and power consumption by implementing gyro filter, integrator, fuzzy block and multirate PID controller with embedded SW. Besides, this design approach would provide additional functions such as memory, PWM driving IPs even with the overall same area as contemporary SoCs. Finally, it was measured that the new OIS controller SoC would offer the decreased operation current of 30%∼53%, with respect to existing SoCs.

Keywords:

OIS, Gyroscope, Motion estimation, Motion Compensation, SoC키워드:

광학식 손떨림 보정, 자이로스코프, 움직임 추정, 움직임 보상, 시스템 온 칩Ⅰ. 서 론

최근 스마트폰 카메라의 고성능화 추세에 따라 고화소의 이미지 센서가 장착되고 있으며, 고화소 센서의 경우 픽셀 사이즈의 소형화 및 민감도가 높은 밝은 렌즈를 적용함에 따라 손떨림에 의한 영상의 화질 열화(Blur) 현상이 더욱 커지게 되었다. 이에 따라 노출 시간이 길어지는 저조도 환경에서의 영상 촬영 시 손떨림을 보정하는 기술이 스마트폰에 확대 적용되기 시작하였다. 또한 줌 기능을 통한 영상을 확대하게 되면 손떨림양도 비례적으로 증가하기 때문에 손떨림 보정 기술은 스마트폰의 필수 사양으로써 적용되고 있다[1, 2].

최근 super resolution[3] 및 image fusion[4] 기술 등을 이용한 고화소의 영상 및 선명한 화질을 구현하는 멀티 카메라 기술이 스마트폰에 적용되고 있다. 두 개의 영상을 병합 시 원본 화질의 열화를 최소화해야만 만족할 만한 성능을 얻을 수 있다. 따라서 멀티 카메라에서의 손떨림 보정 기술은 매우 중요하며, 두 개 이상의 카메라를 사용함에 따라 소모전력이 증가하고, 면적이 커지며, 비용이 증가하는 등의 문제가 대두되고 있다.

본 연구에서는 최신 스마트폰의 사양을 위한 손떨림 보정기술인 광학식 손떨림 보정(Optical Image Stabilization, OIS) 제어 시스템을 저전력 및 저복잡한 컨트롤러 SoC로 설계 및 구현하기 위한 다양한 방안들을 탐색하고 검증하고자 한다. OIS 제어 시스템은 손떨림양을 감지하기 위한 자이로스코프, 움직임 양을 각도로 산출하기 위한 움직임 검출부, 렌즈 구동을 위한 액츄에이터 및 이를 구동하기 위한 움직임 보정부 등으로 구성되어 있다. MEMS 기반의 자이로스코프는 바이어스 오프셋 및 드리프트 등의 오류 성분을 포함하고 있어서 이를 적절히 필터링하고 적분하여야 한다. 본 연구에서는 연산 복잡도가 낮으면서도 정확도가 우수한 BACF/DCF 필터[5] 및 퍼지연산[6]을 이용한 방법을 적용한다. 또한 자이로스코프의 샘플링 주파수를 가변하면서 전력소모에 관한 영향을 분석한다. 액츄에이터의 구동전력을 낮추기 위하여 구동전압 가변 및 펄스폭 변조(Pulse width modulation, PWM) 구동방식을 고려할 수 있으나, 구동전압 가변은 액츄에이터의 기구적 설계 변경을 필요로 하기에 본 연구에서는 PWM 구동 방식을 적용한다. PWM 구동 시 발생할 수 있는 전원 노이즈 및 영상 노이즈를 저감할 수 있는 방안에 대하여 탐색한다. 움직임 보정부의 전력소모를 낮추기 위하여 동작속도를 가변하면서 시스템 응답성능을 확인한다. 움직임 보정부의 면적을 최소화하기 위하여 AD/DA 변환기의 최적의 비트폭을 설계한다. 본 연구에서는 기존 상용 OIS 컨트롤러 SoC 제품의 성능을 면적, 전력소모, 연산장치, 메모리 등의 관점에서 분석하고 이를 기반으로 SoC 설계 목표사양을 결정한다.

본 논문의 구성은 2장에서 스마트폰의 OIS 카메라 및 컨트롤러 SoC 사양을 분석하고, 3장에서 OIS 컨트롤러 SoC 데이터패스를 설계하고, 알고리즘 및 하드웨어 IP로 구성된 SoC 아키텍쳐를 설계한다. 4장에서 OIS 컨트롤러 SoC의 저전력/저복잡도를 위한 방안의 성능을 각각 검증하고, 설계된 OIS 컨트롤러 SoC를 스마트폰의 카메라 모듈에 장착하여 모바일 성능을 검증하고, 마지막 5장에서 결론을 맺는다.

Ⅱ. 스마트폰의 OIS 컨트롤러 SoC 설계

OIS 카메라 시스템의 사양을 분석하고, SoC의 데이터패스 탐색 및 최적화 설계를 통하여 스마트폰에 적합한 저전력 및 저복잡의 OIS 컨트롤러 SoC를 설계한다.

2-1 기존 OIS 카메라 및 컨트롤러 SoC 사양

스마트폰에 적용되는 카메라 시스템의 주요 파라메터는 표 1과 같이 정의할 수 있으며, 1300만 화소 또는 그 이상의 고화소 카메라에 적용되는 주요 값으로 설정하였다.

| (1) |

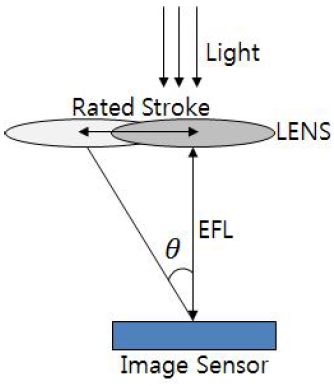

그림 1의 렌즈의 이동거리(Rated stroke)는 보정 각도(Compensation angle, θ) 및 렌즈의 EFL (Effective Focal Length) 사양에 따라서 식(1)과 같이 산출된다. 보정각도 ±1°, EFL 4mm 조건 하에서 렌즈의 이동거리는 ±70μm 으로 설정된다. 손떨림 보정성능을 1pixel 이하로 목표하기 위해서는 Linearity, Hysteresis, Sensitivity, Step response 등 액츄에이터의 동특성을 고려하여 렌즈 Pixel size의 1/10 인 0.1μm 단위로 구동이 가능해야 한다. 따라서 이동거리 ±70μm 을 최소 단위 0.1μm 단위로 구동하기 위해서는 최소 700code 이상의 구동 분해능(Driving sensitivity)을 요구하며, Full stroke 200μm을 기준으로 0.1μm 단위로 위치를 검출해야 하기 때문에 검출 분해능(Sensing sensitivity)은 2,000code 이상을 필요로 한다. 따라서 DA 변환기는 최소 10비트, AD 변환기는 최소 11비트 이상으로 각각 설계되어야 한다.

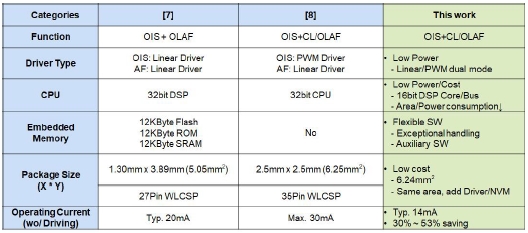

스마트폰에 적용되고 있는 OIS 시스템의 대표적인 상용 SoC로는 [7, 8] 등이 적용되고 있으며, 주요 특징은 표 2와 같다. [7]은 32비트 DSP Core를 내장하고, 12Kbyte의 ROM/SRAM/Flash 메모리, 12비트 4채널 AD 변환기, 8비트 DA 변환기, 홀 앰프, 자이로스코프 출력을 받아들이기 위한 SPI 인터페이스 그리고 액츄에이터 구동을 위한 3채널 (X/Y/Z축) 구동부 등을 갖추고 있다. [7]은 27핀 WLCSP 패키지로, 칩 사이즈는 1.30mm ☓ 3.89mm ☓ 0.33mm로 구성되어 있다. [8]은 32비트 RISC Core를 내장하고 있으며, 12비트 3채널 AD 변환기, 홀 앰프, SPI 인터페이스 그리고 액츄에이터 구동을 위한 3채널 구동부 등을 포함하고 있다. [8]은 35핀 WLCSP 패키지로, 칩 사이즈는 2.50mm☓2.50mm☓0.55mm로 구성되어 있다. AF (Auto Focus) 구동부로써 [7]은 Open loop (OL) 구동을 지원하고, [8]은 Closed loop (CL)와 OL을 지원한다. [8]은 IC 내부에 프로그램을 저장하기 위한 메모리를 가지고 있지 않다. 따라서 동작 초기에 외부 메모리로 부터 프로그램을 다운로드하기 위한 초기 지연 시간이 발생하게 되며, [7]은 IC 내부에 메모리를 내장하여 초기 지연 시간을 해결하고 있다. 동작 시 소모전류는 [7]의 경우 typ. 20mA를 소모하며, [8]은 max. 30mA를 소모한다.

본 연구에서는 OIS 구동을 위한 X/Y 축 드라이버는 선형구동과 PWM 구동을 지원할 수 있게 설정하며, AF를 위한 Z 축은 선형구동을 지원하게 설정한다. IC 사이즈는 [8]의 체적 6.25mm2 보다 작게 목표한다. 메인 코어는 32bit 이하로 타겟하며, 내장 메모리는 [7]의 12KByte 보다 용량을 증가시켜 16KByte로 설정한다. 동작 전류는 [7]의 typ. 20mA 보다 적은 전류소모를 목표로 한다.

2-2 스마트폰 OIS 컨트롤러 SoC 저전력/저복잡 설계

OIS 컨트롤러 SoC의 저전력 설계를 위하여 자이로스코프의 적절한 샘플링 레이트(fs)를 탐색하고, 구동부/제어부의 동작 주파수(fc)를 탐색하며, 액츄에이터의 구동전력을 저감하기 위한 방안을 검토한다. 저복잡 설계를 위하여 복잡도가 낮으면서 정확도가 우수한 자이로 필터를 탐색하고, AD/DA 변환기의 최적 비트폭을 설계한다.

(1) 샘플링 레이트(fs) 탐색

자이로스코프의 적절한 샘플링 레이트(fs)를 설정하기 위해서는 손떨림의 주파수 성분을 분석하고, 카메라의 프레임 레이트 및 자이로 필터의 연산과정까지 고려해야 한다. 모바일 카메라의 손떨림 주파수는 카메라의 panning 동작과 손떨림 동작을 가했을 때 최대 30Hz 이하의 주파수 대역에 분포하고 있다[9]. 샘플링 레이트를 손떨림 주파수 성분만을 고려 시 최대 주파수 30Hz의 두 배인 60Hz로 설정할 수 있다. 또한 카메라의 프레임 단위의 손떨림 보정이 이루어져야 하기 때문에, 이미지 센서의 프레임 레이트를 함께 고려해야 한다. 최근 120fps (Frame per Second)의 고속 프레임을 지원하는 센서들이 연구가 진행되고 있다[10]. 따라서 고속 프레임 레이트를 고려하여 120fps의 두배인 240Hz 이상으로 설정해야 한다. 또한 자이로 필터는 자이로스코프의 출력 값을 이동 평균(moving average)을 이용하여 연산을 진행하기 때문에, 지금까지 논의 된 최대 주파수의 두배 정도, 즉 최소 500Hz 이상으로 설계해야 한다.

(2) 제어 주파수(fc) 탐색

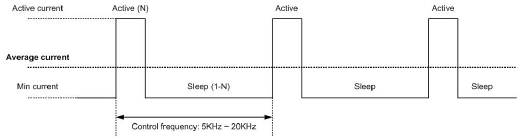

제어 주파수(fc)는 제어부(PID 제어기)와 액츄에이터 구동부의 적절한 동작 속도를 탐색하여 설정한다. 그림 2 및 식(2)에서는 제어 주파수에 따른 평균 전류소모에 대하여 도식하였다. 실제 컨트롤부와 구동부가 동작하는 Active 구간의 시간을 N으로 설정하고, Sleep 구간의 시간을 1-N으로 설정, Sleep 구간에서의 소모전류가 무시할 수 있을 만큼 작다고 가정하면(iSleep ≅ 0), 제어 주파수에 따른 평균 소모전류는 비례적으로 증가함을 알 수 있다. 제어 주파수(fc)는 자이로스코프의 샘플링 레이트(fs)의 최소 500Hz를 고려해서 두배 이상인 1kHz 이상으로 설정해야 하며, 일반적으로 액츄에이터의 고유 주파수(Resonance Frequency)는 약 100Hz 내외의 1차 공진 주파수를 가지고 있으며, 500Hz에서 5kHz 구간에서 2차, 3차 공진 주파수를 가지고 있다. 따라서 제어 주파수(fc)는 최소 5kHz 이상으로 설계해야 한다.

| (2) |

(3) 액츄에이터 구동 방식 탐색

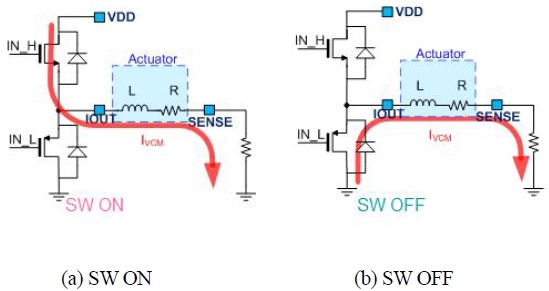

액츄에이터의 구동전력을 저감하기 위해서 구동부의 스위칭 소자를 이용한 구동 방식에 대한 적용 방안을 탐색한다. 액츄에이터를 구동 방식은 일반적으로 선형 구동(Linear driving)과 PWM (Pulse Width Modulation) 구동으로 나누어지며, 전력효율 측면에서 PWM 구동이 효과적이다[11]. PWM 구동은 액츄에이터의 인덕턴스 성분(inductive load)을 이용하여 구동된다. PWM 구동 회로는 그림 3과 같이, PMOS와 NMOS의 조합으로 구성된다. 그림 3(a)와 같이 상단 PMOS가 턴온되면 VDD로 부터 액츄에이터로 에너지가 공급되고, 그림 3(b)와 같이 PMOS가 턴오프되고 NMOS가 턴온되면 액츄에이터 내부의 인덕턴스 성분에 의하여 충전된 에너지를 방전하면서 액츄에이터를 구동하게 된다. 따라서 에너지를 방전하는 구간에서는 외부 배터리의 전류를 소모하지 않게 되어, 소모전력을 절약할 수 있게 된다.

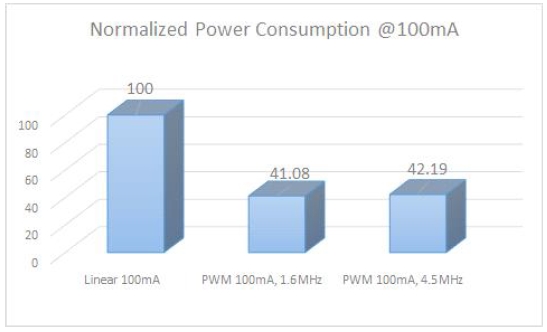

그림 4는 선형 구동 대비 PWM 구동 시 전력 소모를 시뮬레이션한 결과이다. 시뮬레이션 조건은 구동전압 2.8V, 액츄에이터 저항 10ohm, 인덕턴스 10μH로 가정하였고, 액츄에이터 구동 전류 100mA 구동 및 PWM 주파수 1.6MHz/4.5MHz 로 구동한 경우이다. 선형 구동 대비 PWM 구동은 50% 이상의 전력이 절감됨을 알 수 있다. PWM 구동은 선형 구동 대비 전력소모가 적은 장점이 있지만, PWM 구동으로 인한 노이즈를 해결하기 위한 연구가 필요하다. 노이즈를 저감하기 위한 [12] 연구에서는 전원단 소자의 배치 및 레이아웃을 고려하였다. 스위칭 소자를 사용하는 반도체[13]의 경우 전원단의 PCB 패턴 및 면적/길이에 대하여 가이드하고 있다. 본 연구에서는 [12, 13] 등의 연구를 기반으로 노이즈를 저감할 수 있는 설계를 수행하고 실험적으로 검증한다.

OIS 컨트롤러 SoC의 저복잡 설계를 위하여 성능대비 연산량을 최적화한 자이로 필터를 설계하고, AD/DA 변환기의 비트폭을 최적화 설계한다.

(1) 낮은 연산량의 자이로 필터 설계

MEMS 기반 자이로스코프는 변화량을 측정하는 과정에서 잡음이 발생하게 되어 출력 값에 오차를 포함하게 된다. 따라서 자이로 필터는 바이어스 드리프트 및 오프셋 에러를 제거하기 위한 기능을 수행하면서도 저복잡도의 필터를 설계해야 한다. 저복잡도의 자이로 필터를 구현하기 위하여 구조가 간단하고, 모바일 카메라에 적용이 가능한 성능의 BACF/DCF 및 퍼지부를 결합하여 필터를 설계한다[5, 6]. BACF/DCF는 복잡한 예측없이 추정과정으로만 구성되어 낮은 연산량과 복잡도를 갖지만, 고정 이득 값을 적용하여 정지 상태 드리프트에 대한 보정성능은 우수하지만 급격한 변화에는 낮은 보정성능을 가진다. 이러한 급격한 손떨림 변화를 구별하여 적절한 제어 처리를 수행하기 위하여 퍼지부를 추가한다. 퍼지부는 간단한 룰기반의 모델로 사용자의 손떨림 상태와 예외 상태를 구분한다.

(2) AD/DA 변환기 비트폭 최적화

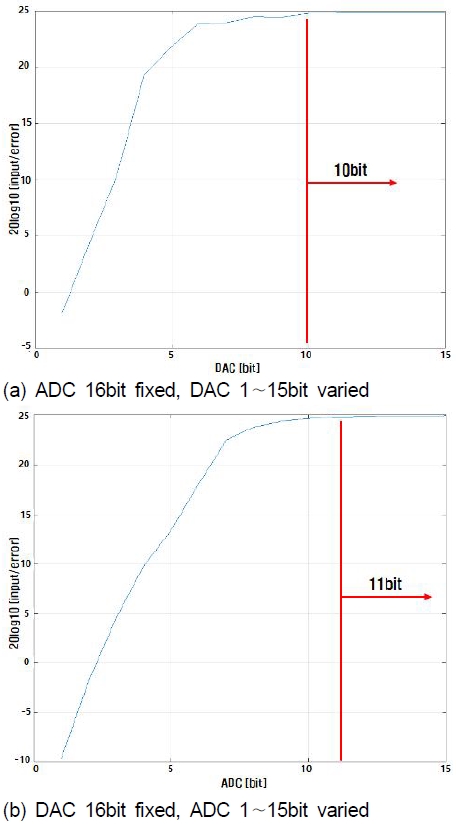

시스템 사양 분석을 통하여 구동 분해능(DAC resolution)은 최소 700 code, 검출 분해능(ADC resolution)은 최소 2,000 code 의 분해능이 필요함을 확인하였다. 이를 기준으로 정수 연산 시뮬레이션을 통해서 AD/DA 변환기의 비트폭을 가변하면서 양자화 오류를 측정하여 비트폭을 탐색한다. 비트폭 가변에 따른 시스템 최적의 성능을 평가하기 위하여, 상용 DSP Core 및 상용 16비트 AD/DA 변환기를 이용한다. 16비트 AD/DA 변환기 각각의 데이터를 DSP Core 상에서 LSB (Least Significant Bit)를 삭제(truncation)하면서 비트폭을 가변해서, 가변 비트폭에 대한 에러양을 확인하여, 이를 입력 대비 오차의 크기를 비례적으로 정량화하였다. AD 변환기의 데이터를 16비트로 고정 후 DA 변환기의 데이터 비트를 가변한 결과 그림 5(a)와 같이 10비트에서 에러가 최소 값으로 수렴하며, DA 변환기 데이터를 16비트로 고정 후 AD 변환기 데이터 비트를 가변한 결과 그림 5(b)와 같이 11비트에서 최소 에러가 수렴하는 것을 확인할 수 있다. 이에 따라서 DA 변환기 10비트, AD 변환기 11비트를 최적 설계 값으로 설정할 수 있다.

Ⅲ. OIS 컨트롤러 SoC 아키텍쳐

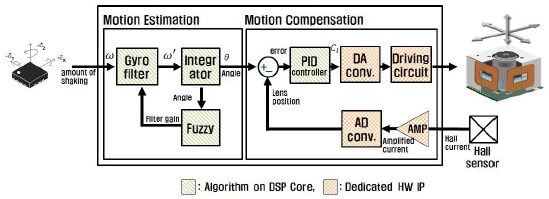

OIS 컨트롤러 SoC는 그림 6과 같이 움직임 검출부, 움직임 보정부로 구성된다. 녹색으로 표시 된 자이로 필터, 적분기, 퍼지부, 제어기 등은 DSP Core의 임베디드 SW 알고리즘으로 설계되었으며, 노란색으로 표시 된 AD/DA 변환기, 구동부, 홀 앰프 등은 전용 HW IP로써 설계되었다.

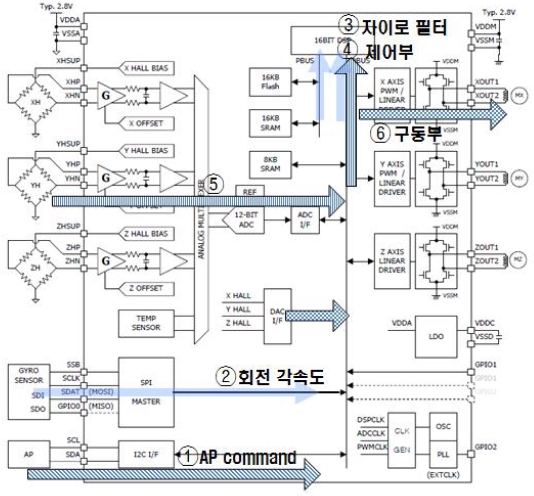

3-1 OIS 컨트롤러 SoC 데이터패스

OIS 컨트롤러 SoC는 전원이 인가되면, LDO에서 내부 전원을 설정하고, OSC, PLL에 의해서 DSP CLK, ADC CLK, PWM CLK 등이 생성된다. OIS 컨틀롤러 SoC의 데이터패스는 그림 7의 ①∼⑤ 경로와 같이 구성된다. ①AP 명령어는 AP로 부터 I2C로 초기셋팅 및 OIS 제어명령 등을 입력받고, DBUS를 통하여 DSP Core에 전달되어 손떨림 보정 동작을 시작하게 된다. ②회전 각속도는 자이로스코프로 부터 출력된 각속도(w)를 SPI로 입력받고, 입력된 데이터를 DBUS를 통하여 DSP Core에 전달한다. DSP Core는 입력된 각속도 데이터에서 ③자이로 필터를 통해서 바이어스 오프셋과 드리프트를 제거하고 적분 연산을 수행하여 회전각 데이터(θ)를 생성하고, ④제어기에서는 회전각 데이터(θ)와 액츄에이터로 부터 출력된 렌즈위치를 입력받아 제어값(ci)을 생성한다. 액츄에이터 내부의 홀 센서는 ⑤와 같이 렌즈의 현재 위치를 전압으로 출력하고, 이를 홀 앰프에 전달하여 증폭된 신호를 생성하고, 아날로그 먹스를 거쳐서 AD 변환기에 입력된다. AD 변환기에서 코드값으로 변환되어진 렌즈 위치값은 DBUS를 통하여 제어기로 전달된다. 제어기(PID controller)에서 생성된 ⑥액츄에이터의 제어값은 DA 변환기를 거쳐 구동부로 전달되어 액츄에이터를 구동하게 된다.

3-2 OIS 컨트롤러 SoC 설계

OIS 컨트롤러 SoC를 설계하기 위하여 DSP Core에 그림 8의 자이로 필터, 적분기, 퍼지부 및 제어부 등을 임베디드 SW로 설계하고, 움직임 보정부의 구동회로, AD/DA 변환기 및 홀 앰프 등을 전용 HW 회로로 설계한다.

DSP 코어 임베디드 SW의 알고리즘은 자이로 필터, 적분기, 퍼지부 및 제어부 등의 데이터패스로 그림 8과 같이 구성된다.

(1) 움직임 검출부 알고리즘

자이로스코프로 부터 손떨림 정보를 회전각속도(w)로 입력받아, BACF/DCF 및 퍼지기반의 필터를 이용하여 식(3), 식(4)와 같이 바이어스 오프셋(ϵoffset)과 드리프트(ϵdrift)를 제거한 신호(w′)를 적분기 및 퍼지부로 출력한다. 오차가 제거된 손떨림 신호(w′)는 적분기에 입력되어 손떨림 각도(θ)로 변환되고 움직임 보정부와 퍼지부로 출력된다. 퍼지부는 DCF 이득(GDCF)을 자이로필터로 입력시켜서 손떨림 주파수에 대한 위상 오차를 보상한다.

| (3) |

| (4) |

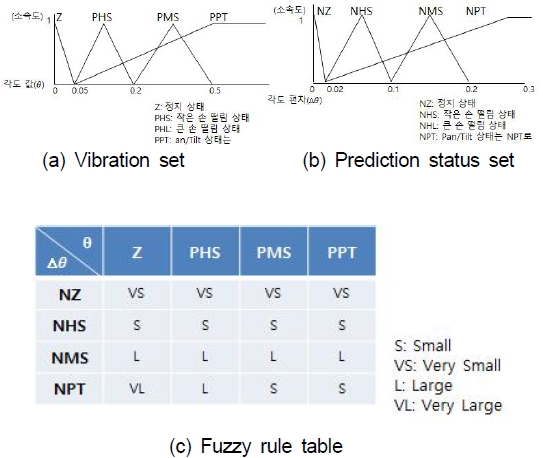

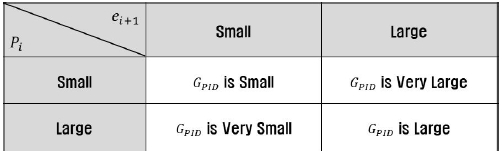

퍼지부는 그림 9와 같은 손떨림 집합(a), 예측 상태 집합(b)에 기반한 퍼지 룰 테이블(c)를 이용하여 DCF 이득(GDCF)을 연산하여 자이로 필터로 출력한다.

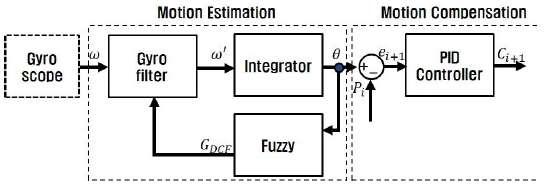

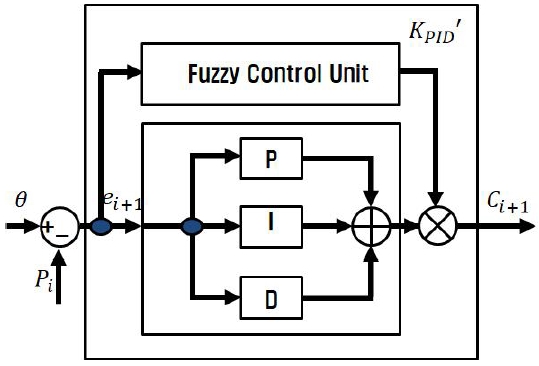

(2) 멀티레이트 PID 제어기

제어부는 PID 제어기와 퍼지 제어기로 이루어진 멀티레이트(Multirate) PID 제어기는 그림 10과 같이 구성되어 있다. 제어기는 움직임 검출부에서 출력된 손떨림 각도(θ) 및 액츄에이터의 홀센서에서 출력된 현재 렌즈의 위치 값(Pi)이 제어기에 입력된다. 이 두개의 값을 차분한 값(ei+1)을 이용하여 액츄에이터를 구동하기 위한 제어값(ci+1)을 산출한다.

퍼지 제어기는 오차 값(ei+1) 및 움직임 검출부에서 출력 된 GPID 그리고 손떨림 상태(Q)를 기반으로 현재 제어기의 상태를 표 3의 룰테이블에 따라 판단한다. 판단된 상태에 따라 PID 제어기의 이득(GPID′) 값을 조정하여 액츄에이터의 구동 특성을 개선한다. 그리고 손 떨림 상태(Q)를 구별하여 PID 제어기의 이득 값(GPID′)의 범위를 다르게 하기 때문에 효율적인 임베디드 SW 제어를 수행할 수 있게 된다.

움직임 보정부의 구동기, AD/DA 변환기 및 홀 앰프 등을 전용 HW IP로 설계한다.

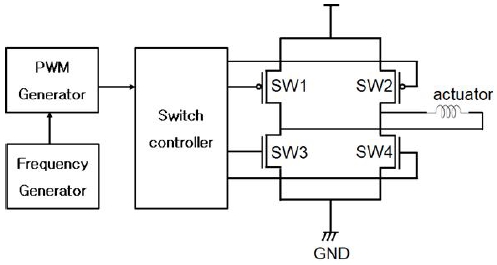

(1) 액츄에이터 구동회로

움직임 보정부의 구동기는 DA 변환기의 출력을 입력으로 받아 PWM 발생기(PWM generator)를 이용하여 적절한 듀티(Duty) 값 생성을 하기 위한 제어 신호를 스위치 제어기로 출력한다. 스위치 제어기에서는 H-브릿지를 제어하여 액츄에이터를 구동하게 된다. H-브리지 회로는 그림 11과 같이 NMOS, PMOS의 조합으로 구성되어 있으며, 스위치 제어기에서 출력되는 제어신호를 입력받아 각각의 스위치(그림 11 SW1∼4)를 on/off 하여 제어한다[12].

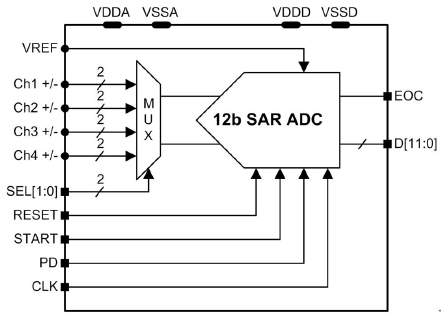

(2) AD 변환기 및 홀 앰프

AD 변환기는 그림 12와 같이 12비트의 SAR (Successive Approximation Register) 타입 ADC[14]와 4개 채널의 아날로그 먹스(analog MUX)로 구성되어 있다. 입력전원은 3.3V 아날로그 전원(VDDA/VSSA)과 1.2V 디지털 전원(VDDD/ VSSD)을 입력으로 받는다. AD 변환기의 기준 전압은 VREF로 입력되며 dynamic range는 VDDA까지 입력 가능하다. 차동 아날로그 입력 신호인 Ch1 +/- ∼ Ch4 +/- 는 VSSA에서 부터 VREF까지 입력 가능하다. Ch1∼Ch3는 액츄에이터의 X/Y/Z 축의 홀 센서의 출력이 연결되며, Ch4는 온도센서의 출력이 연결된다.

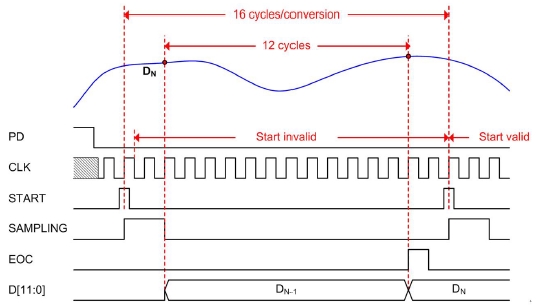

AD 변환기의 동작 타이밍은 그림 13과 같다. START 신호가 인가되고, 2 클록 동안 입력 전압에 대한 sample과 hold가 진행된다. 이후 12 클록 동안 변환이 진행되고, EOC (End of Conversion) 신호가 출력된다. 따라서 START 신호가 인가 된 이후 16 클록 이후에 유효한 변환된 데이터가 D[11:0]에 실리게 된다.

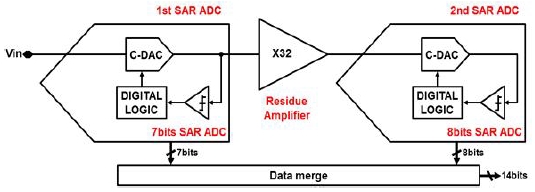

AD 변환기는 그림 14와 같이 2단 파이프라인 구조로 구성되어 있다. 1단계는 7비트 SAR ADC로 구성되며, 2단계는 8비트 SAR ADC로 구성된다. 1단계와 2단계에서 각각 7비트, 8비트의 AD 변환 결과를 결정하고, 1단계의 LSB와 2단계의 MSB를 중첩시켜 데이터를 출력한다.

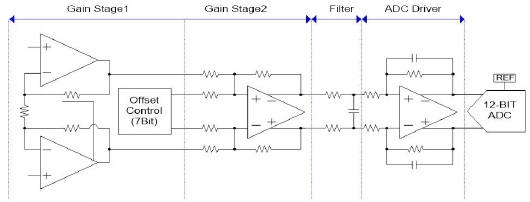

홀 앰프 블록은 그림 15와 같이 Gain Stage1, Gain Stage2, Filter, ADC driver 로 구성되어 있다. Gain stage1은 게인을 4x, 8x로 가변 가능하며, Gain stage2는 1x∼12x로 가변 가능하도록 설계되었다.

Ⅳ. 실험 및 고찰

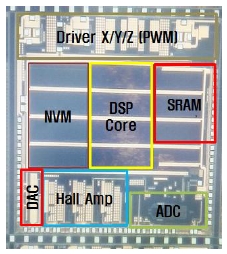

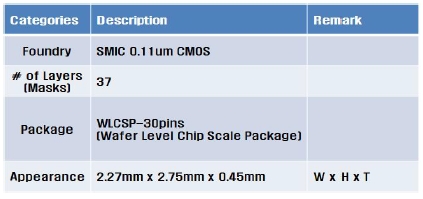

모바일 OIS 컨트롤러 SoC는 표 4와 같이 37개 layer (mask)로 구성된 SMIC 0.11μm CMOS 공정으로 제작되었다. 제작된 IC의 패키지(Package) 형태는 WLCSP (Wafer Level Chip Scale Package) 타입으로 6×5핀 배열의 총 30핀으로, 2.27mm×2.75mm ×0.45mm 크기로 제작되었다. 제작된 칩의 실물은 그림 16과 같이 Driver(구동부), NVM(메모리), DSP Core, SRAM, DAC, Hall amp, ADC 등으로 구성되어 있다.

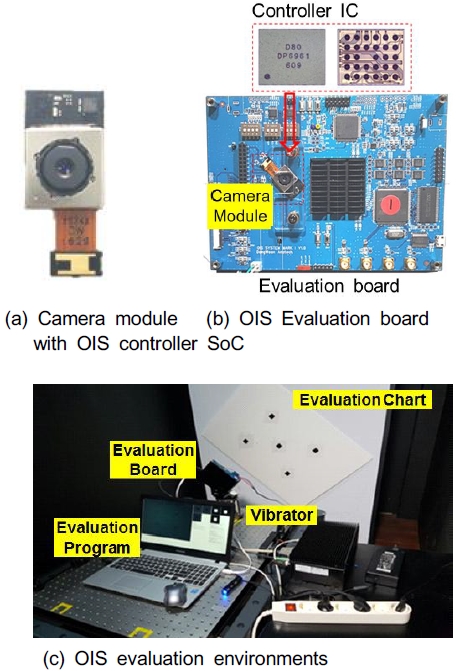

성능 평가를 위하여 그림 17과 같이 OIS 컨트롤러 SoC를 실장한 카메라 모듈(a)을 평가보드(b)에 장착하고, 모바일 OIS 컨트롤러 SoC 평가환경(c)을 구성한다. OIS 컨트롤러 SoC 성능검증을 위하여 손떨림 각도 오차와 손떨림 주파수에 대한 위상 오차에 대한 보상 성능을 확인하기 위하여 영상을 촬영하고 PWM 구동에 따른 노이즈 평가 및 손떨림 보정된 영상의 화질을 평가한다.

4-1 OIS 컨트롤러 SoC 성능 비교

본 연구에서 설계된 OIS 컨틀로러 SoC와 기존 상용제품 [7, 8]을 비교한 사양은 표 5와 같다. 구동기는 PWM 구동 및 선형구동을 동시에 지원할 수 있도록 설계하여 사용자가 선택할 수 있도록 하였으며, 노이즈를 방지할 수 있는 방안으로도 활용될 수 있도록 하였다. 임베디드 CPU는 기존 32비트 Core에 16비트 DSP Core 및 버스를 적용하여 면적 및 전력소모를 개선하였다. 내장 메모리는 [7]의 12KByte 보다 확장된 16KByte NVM을 포함시켜 추가적인 자이로 필터 알고리즘이나 예외처리에 대한 대응을 임베디드 SW로 효과적으로 처리할 수 있도록 설계되었다. 면적은 [8]과 유사한 수준이나 구동부의 PWM/선형 구동지원 및 내장메모리 등이 탑재되어, 동일 면적에서 다양한 기능을 추가적으로 지원할 수 있다. 액츄에이터의 구동전력을 제외한 operating 전류는 기존 제품들과 비교해서 약 30%∼53% 감소한 것으로 확인되었다.

4-2 OIS 컨트롤러 SoC 성능 검증

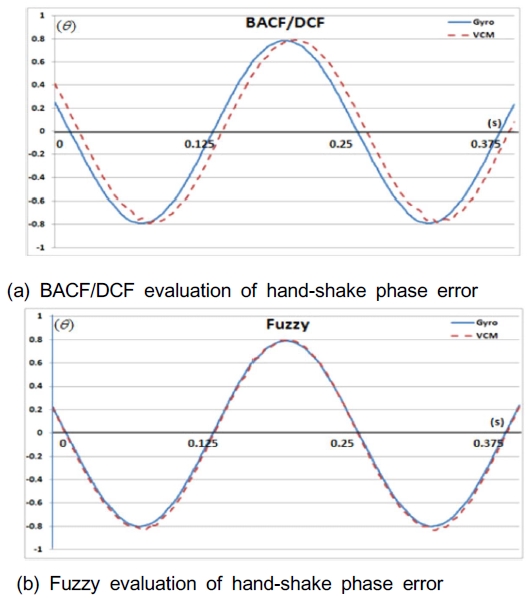

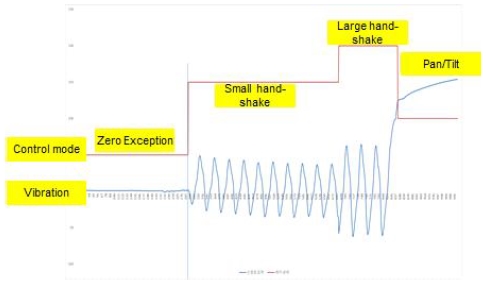

(1) 임베디드 SW 자이로 필터

내장된 16비트 DSP Core 및 16KB NVM을 기반으로 효과적인 자이로 필터 알고리즘을 임베디드 SW로써 구현할 수 있다. 자이로 필터의 보상 성능을 검증하기 위하여 BACF/DCF로 자이로 필터를 구성한 경우와 이에 퍼지부를 추가한 경우에 대하여 검증하였다. 그림 18은 위상 오차 보상 성능을 검증한 결과로써, 가진각 ±0.8도, 가진 주파수 4Hz에서의 BACF/DCF와 퍼지를 추가한 알고리즘의 위상 보상 결과 값을 자이로스코프의 출력값과 실제 액츄에이터의 렌즈변위를 비교해서 보이고 있다. 퍼지기반 위상 오차 보상 알고리즘을 통해서 손떨림 입력신호와 움직임 보정부의 보상 값 사이의 위상 오차가 개선되었음을 확인할 수 있다. 또한 스마트폰 고유 환경을 위해서 모바일 OIS 시스템의 안정성을 개선하기 위한 다양한 손떨림 상태 검출 성능을 측정하였다. 가진기를 이용하여 가변적인 손떨림 진동을 인가하고, 손떨림 상태 검출 결과를 확인한 결과는 그림 19와 같다. 퍼지기반 손떨림 상태 검출 알고리즘이 가진기를 통하여 입력된 진동에 대해서 손떨림 상태를 적절하게 검출하는 것으로 확인되었다.

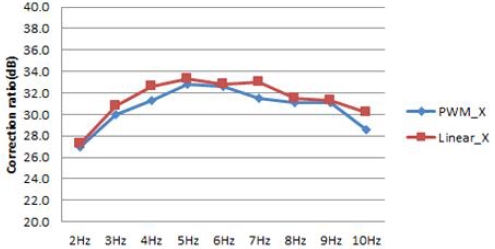

(2) PWM 구동회로 노이즈저감 설계

액츄에이터의 PWM 구동에 따른 손떨림 보정 성능은 그림 20과 같이 PWM 구동 주파수를 2MHz로 고정하고 주파수를 2Hz∼10Hz 까지 가변하면서 억압비에 대한 성능을 확인하였다. 선형 구동 대비하여 최대 -2dB 정도의 차이를 확인하였으며, PWM 구동이 선형 구동과 유사한 성능을 보임을 알 수 있다.

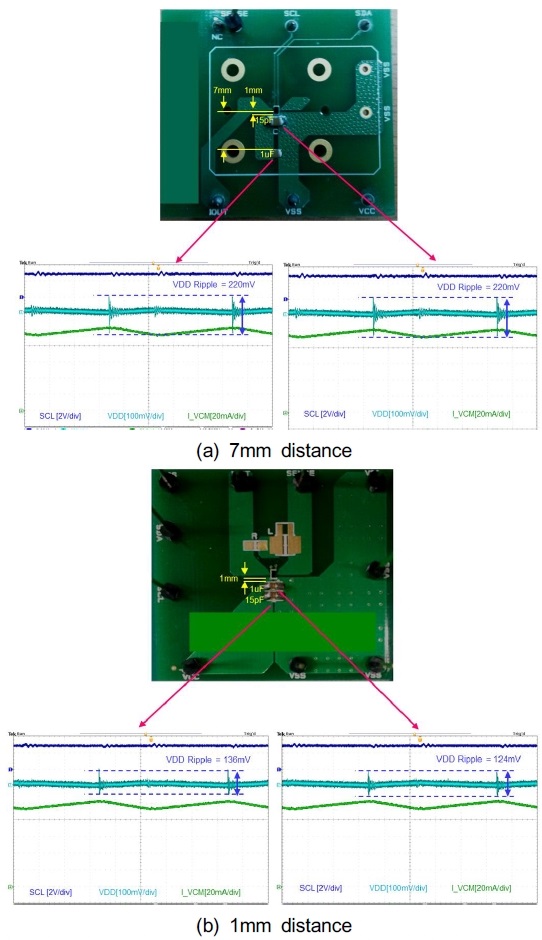

PWM 구동 시 발생할 수 있는 전원 노이즈와 영상노이즈를 저감할 수 있는 방안을 검증하고, PWM 구동 시 전력효율과 동작 성능을 검증한다. PWM 구동에 따른 전원 노이즈를 분석하기 위하여 그림 21과 같이 decoupling capacitor와 IC 거리를 7mm, 1mm의 경우를 검증하였다. 이격 거리 7mm 시 VDD ripple이 220mV 가 발생하였으며, 1mm로 조정 시 VDD ripple이 136mV로 저감되는 것을 확인하였다. 따라서 PWM 구동에 따른 전원 노이즈 저감을 위해서는 IC와 decoupling capacitor와 거리를 최대한 가깝게 배치해야 한다.

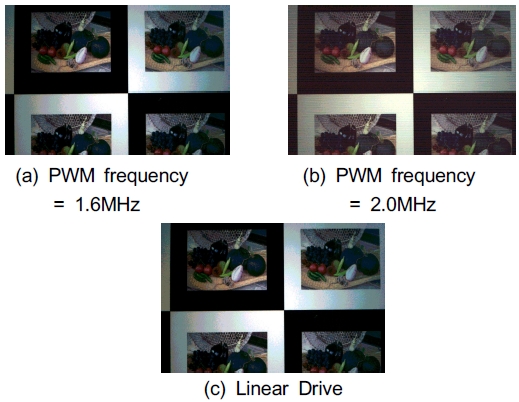

PWM 구동에 따른 영상 노이즈를 평가하기 위하여 PWM 구동 주파수를 1.6MHz, 2MHz로 가변하여 평가를 진행하였다. 그림 22에서와 같이 영상을 비교하면 PWM 구동 주파수 1.6MHz에서 노이즈 성분이 많이 발생하며, PWM 구동 주파수 2MHz에서 영상 노이즈가 감소하는 것을 확인할 수 있다.

(1) 샘플링 레이트(fs) 최적화

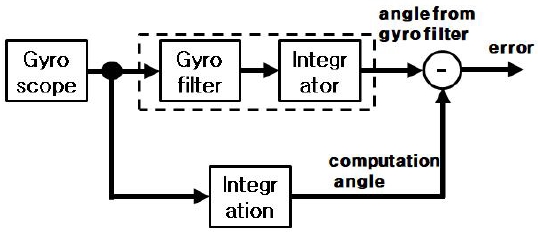

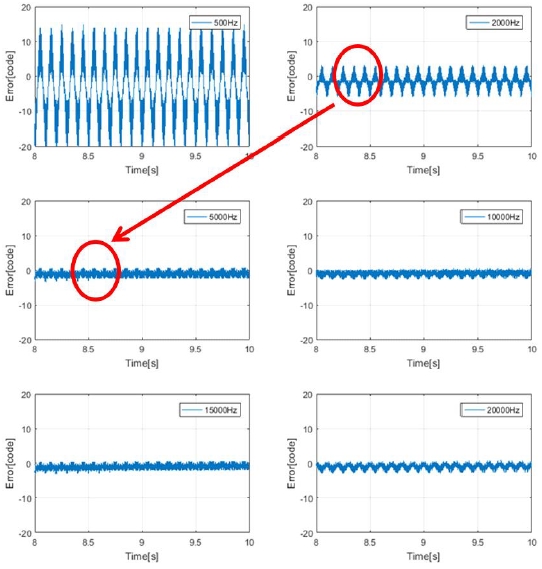

자이로 샘플링 주파수에 따른 광학식 손떨림 보정 SoC의 동작성능을 검증하기 위하여 그림 23과 같은 시뮬레이션 모델을 이용하여 자이로스코프 신호를 입력하고, 자이로 필터와 적분기를 거친 신호 대비 자이로 신호를 부동소수점 연산을 통한 신호를 차분한 에러 값으로 성능을 검증하였다.

자이로스코프 샘플링 주파수(fs)를 500Hz에서 20kHz로 가변하여 실험한 결과, 그림 24에서와 같이 5kHz 이상에서는 에러 값이 크게 변화하지 않는 것으로 검증되었다.

(2) 동작 주파수(fc) 최적화

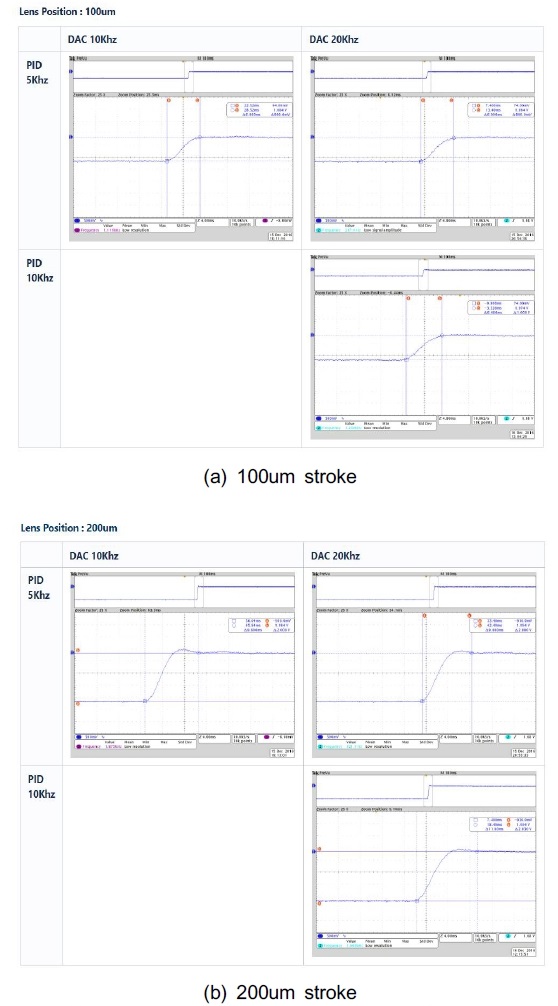

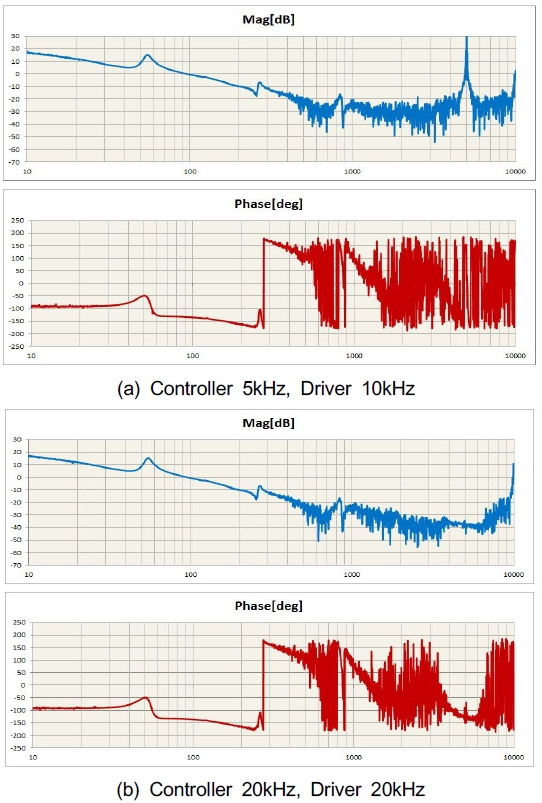

제어부와 구동부의 동작속도 가변에 따른 광학식 손떨림 보정 SoC 성능 평가를 위하여 제어부와 구동부를 5kHz, 10kHz 및 20kHz 로 가변하면서 성능을 측정한다. 액츄에이터를 100μm, 200μm 구동 시 PID 제어기의 동작 특성을 평가한 결과는 그림 25와 같다. 액츄에이터를 100μm 이동 시(그림 25(a)) 제어부 5kHz 기준으로 구동부 10kHz/20kHz로 동작 시 셋틀링 타임은 6ms로 측정되었고, 제어부 10kHz, 구동부 20kHz로 동작 시 셋틀링 타임은 6.5ms로 측정되었다. 액츄에이터를 200μm 이동 시(그림 25(b)), 제어부 5kHz 기준으로 구동부를 10kHz로 동작 시 셋틀링 타임 9.8ms, 오버슛 130μm로 측정되었고, 구동부 20kHz로 동작 시 셋틀링 타임 9ms, 오버슛 100μm로 측정 되었다. 제어부 10kHz, 구동부 20kHz 구동 시 셋틀링 타임 11ms, 오버슛 130μm로 측정되었다. 표 6에 비교한 결과에 따르면 제어부는 5kHz, 구동부는 10kHz까지 낮추어도 성능에 영향이 없는 것이 검증되었다. 또한 제어부/구동부 각 20kHz 로 동작하는 경우와 비교하여 5kHz 제어부 및 10kHz 구동부의 OIS 컨트롤러 SoC의 시스템 응답특성(FRA, Frequency Response Analysis)을 그림 26에서 비교한 결과 이득 마진(Gain margin)과 위상 마진(Phase margin) 등의 시스템 응답특성이 크게 변하지 않는 것으로 확인되었다.

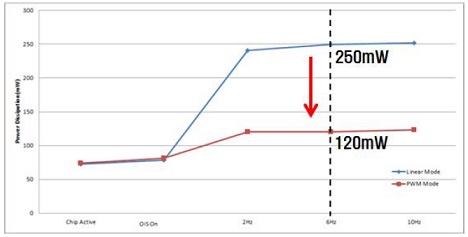

(3) PWM 구동전력 최적화

PWM 구동에 따른 전력 효율은 그림 27과 같다. 가진각도 ±1도, PWM 구동 주파수 2MHz에서 가진 주파수 6Hz 기준으로 선형 구동 시 250mW 정도의 소모전력이 발생하고, PWM 구동 시 120mW로 측정되어 소모전력이 약 50% 이상 감소하는 것을 확인할 수 있다.

움직임 보정부의 소모전력을 낮추기 위하여 PWM 구동을 적용하게 되면 선형구동 대비 유사한 성능을 보이면서도 소모전력은 약 50% 이상 절감되는 것으로 확인 되었다.

4-3 모바일 OIS 카메라 시스템 성능 검증

SoC의 시스템 동작 및 성능 검증을 위해서 스마트폰의 카메라 모듈에 탑재를 하고 가진 테스트, Pan/Tilt 동작 테스트 그리고 영상을 이용한 억압비 평가 등을 진행하였다.

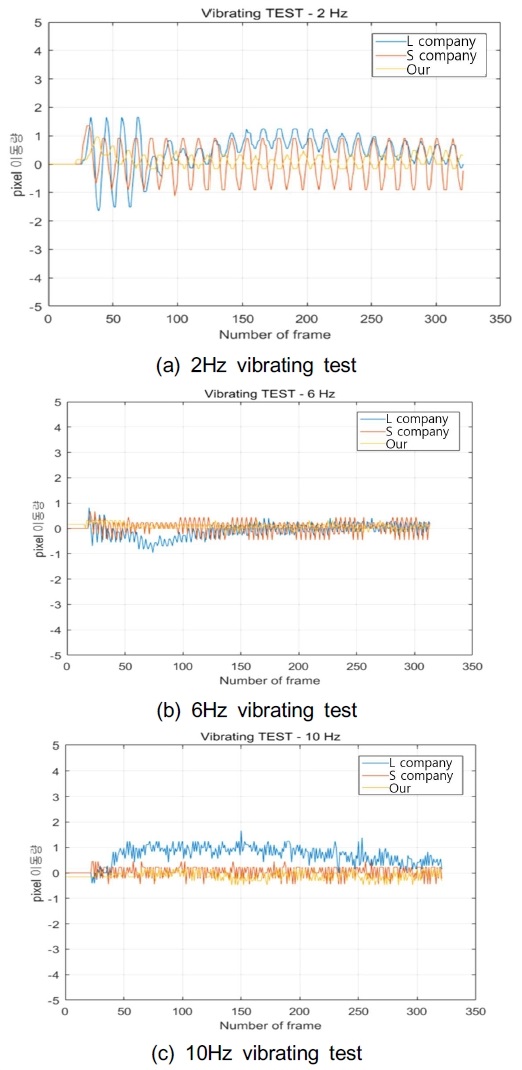

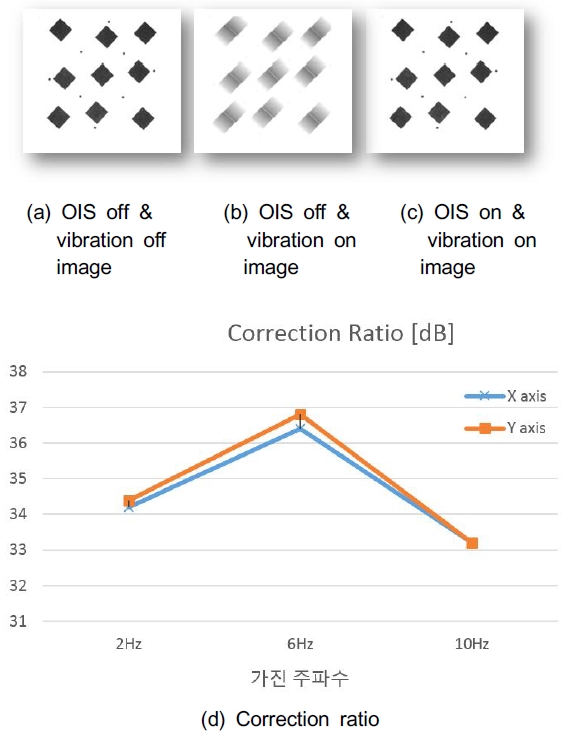

가진 테스트 결과는 그림 28과 같다. 가진기를 이용하여 가진 주파수를 2Hz/6Hz/10Hz 각각의 경우에 대하여 L사, S사 상용제품과 비교 테스트를 진행하였다. L사 제품의 경우 6Hz, 10Hz에서 약간 불안정한 반응을 보였으나, 본 연구 결과물은 모든 대역에서 안정적으로 반응하는 것으로 확인 되었다.

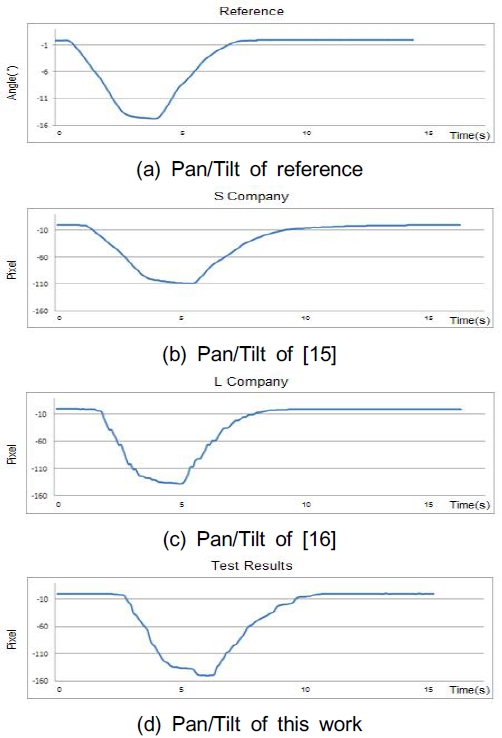

Pan/Tilt 테스트 결과는 그림 29와 같다. 가진기의 출력을 그림 29(a)와 같은 기준 움직임으로 설정하고 이를 상용 제품에 적용하여 측정한 결과는 그림 29(b), (c)와 같으며, 본 연구에서 설계 된 SoC가 탑재된 카메라 모듈의 응답특성은 그림 29(d)와 같다. Pan/Tilt 동작에서 상용제품과 비교할 때 유사한 결과를 보였으며, 영상이 흐르는 이상 동작이나 Pan/Tilt 동작 종료 후 발진과 같은 문제 현상들이 없음을 확인하였다.

억압비(Correction ratio) 평가결과는 그림 30과 같이 X축 기준으로 2Hz에서 34.2dB, 6Hz에서 36.4dB, 10Hz에서 33.2dB로 확인되었으며, Y축 기준으로 2Hz에서 34.4dB, 6Hz에서 36.8dB, 10Hz에서 33.2dB로 평가되었다. 가진 주파수 2Hz에서 10Hz 까지 전 대역 및 X/Y축에 대하여 33dB 이상의 억압비 성능을 나타내는 것으로 확인되었다.

Ⅴ. 결론

본 연구에서는 스마트폰에 적용 가능한 광학식 손떨림 보정 SoC의 저전력, 저복잡 설계를 위한 최적화 방안을 탐색하고 SoC 설계 결과를 통해서 검증하였다. 자이로 샘플링 주파수는 500Hz에서 20kHz까지 가변시켰을 때 5kHz 이상에서 에러 값이 크게 변화가 없는 것을 확인하였다. 움직임 보정부의 제어부와 구동부의 동작속도를 각 5kHz에서 20kHz로 가변하면서 실험한 결과는 제어부 5kHz, 구동부 10kHz 까지 낮추어도 액츄에이터의 동작특성 및 OIS 컨트롤러 SoC의 주파수 응답특성에 문제가 없는 것으로 확인되었다. PWM 구동에 따른 전력 효율은 PWM 구동 주파수 2MHz, 가진 주파수 6Hz 기준으로 선형구동과 비교하여 약 50% 이상 소모전력이 감소하였으며, PWM 구동 주파수별 영상 노이즈를 평가한 결과는 PWM 구동 주파수 2MHz 이상에서 영상 노이즈가 감소하는 것으로 확인하였다. 자이로필터는 연산 복잡도 및 보정성능을 고려하여 BACF/DCF와 적응적 제어를 위한 퍼지부를 결합한 필터를 적용한 결과 손떨림 각도 오차와 위상 오차에 대한 우수한 보상 효과를 확인하였다. AD/DA 변환기의 비트폭을 가변한 결과 AD 변환기는 11비트, DA 변환기는 10비트로 최적화하였다.

본 연구에서 설계된 SoC와 상용제품[7, 8]과의 성능을 비교하면, 면적은 기존 상용제품과 유사한 수준이나 구동부의 PWM/선형 구동 지원 및 내장 메모리 등이 추가 탑재되어 있어, 동일 면적에 더 많은 기능을 지원할 수 있다. 액츄에이터의 구동전력을 제외한 operating 전류는 기존 제품과 비교할 때 약 30%∼53% 감소한 것으로 확인되었다.

Acknowledgments

본 연구는 2016년도 광운대학교 교내학술연구비 지원에 의해 수행되었으며, 본 연구를 위해 지원해 주신 ㈜동운아나텍 대표이사 및 관련 임직원들께 감사드립니다.

참고문헌

- Galaxy S10 [Internet]. Available: https://www.samsung.com/sec/smartphones/galaxy-s10

- P30 [Internet]. Available: https://consumer.huawei.com/en/phones/p30/

-

Sung Cheol Park, Min Kyu Park, Moon Gi Kang, “Super-resolution image reconstruction: a technical overview”, IEEE Signal Processing Magazine, p21-36, (2003).

[https://doi.org/10.1109/msp.2003.1203207]

-

Prashant Rupapara, Aravind Rangavajjula, Anurag Jain, “Low complexity image fusion in bayer domain using a monochrome sensor and bayer sensor”, 2017 IEEE International Conference on Image Processing (ICIP), p1980-1984, (2017).

[https://doi.org/10.1109/icip.2017.8296628]

- S. K. Lee, J.-H. Kong, “The Design and Evaluation of BACF/DCF for Mobile OIS Gyro sensor’s zero point angle following”, The Institute of Electronics Engineers of Korea, Journal of IEEK, 49(8), p16-21, (2012).

-

S. K. Lee, J.-H. Kong, “Design and Implementation of Fuzzy-based Algorithm for Hand-shake State Detection and Error Compensation in Mobile OIS Motion Detector”, The Institute of Electronics Engineers of Korea, Journal of IEEK, 52(8), p29-39, (2015).

[https://doi.org/10.5573/ieie.2015.52.8.029]

- Onsemi, “LC898123”, [Internet]. Available: http://www.onsemi.com/PowerSolutions/product.do?id=LC898123AXD.

- ROHM, “BU24234”, [Internet]. Available: https://www.rohm.com.

-

Hyung Jin Chang, Pyo Jae Kim, Dong Sung Song, and Jin Young Choi, “Optical Image Stabilizing System using Multirate Fuzzy PID Controller for Mobile Device Camera”, IEEE Transactions on Consumer Electronics, 55(2), p303-311, (2009).

[https://doi.org/10.1109/tce.2009.5174385]

-

Toshio Yasue, Kohei Tomioka, Ryohei Funatsu, et al, “A 33Mpixel CMOS imager with multi-functional 3-stage pipeline ADC for 480fps high-speed mode and 120fps low-noise mode”, 2018 IEEE International Solid - State Circuits Conference - (ISSCC), p90-92, (2018).

[https://doi.org/10.1109/isscc.2018.8310198]

- “PWM/linear driver for an electromagnetic load”, Patent No. US6804131B2

- Kai, G., Tsuchiya, S., “DRIVE CIRCUIT AND DRIVING METHOD FOR LINEAR ACTUATOR, LENS MODULE USING THEM AND ELECTRONIC EQUIPMENT”, Patent No. JP05836041B2.

- PCB Layout Considerations, [Internet]. Available: https://www.analog.com/media/en/technical-documentation/application-notes/an136f.pdf

-

HW Shin, JM Jeong, TJ An, JS Park, SH Lee, “A 0.16mm2 12b 30MS/s 0.18um CMOS SAR ADC Based on Low-Power Composite Switching”, Journal of the Institute of Electronics and Information Engineers, p27-38, (2016, Jul).

[https://doi.org/10.1109/isocc.2015.7401641]

- Samsung Galaxy S8 [Internet]. Available:https://www.samsung.com/sec/smartphones/galaxy-s8/

- LG V30, [Internet]. Available: https://www.lg.com/us/v30-phones

저자소개

1980년 : 서울대학교 전자공학과 학사 졸업

1982년 : 한국과학기술원 전기 및 전자공학과 석사 졸업

1989년 : 텍사스 주립대학교 (Austin) 컴퓨터공학과 박사 졸업

1989년~현 재: 광운대학교 소프트웨어융합대학 컴퓨터정보공학부 교수

※관심분야: 영상신호처리 SoC 설계, Embedded Computing System 설계

2002년 광운대학교 컴퓨터공학과학사졸업

2004년 광운대학교 컴퓨터공학과석사졸업

2019년 광운대학교 컴퓨터공학과박사졸업

2006년~현 재: ㈜동운아나텍 기술개발본부 근무

※관심분야: 모바일 카메라 및 프로세서(AP), 영상신호처리(ISP), Embedded Computing System 설계